PCIe TX/RX 物理層信號完整性測試方法詳解

PCIe 既有串行通信接口,又有存儲接口,這 一點與 SAS 和 SATA 不同,因此實現了額外 的行業擴充能力。PCIe 在跟復合 ( 系統 / 主機 ) 與端點 ( 插件 ) 之間基于點到點總線拓撲,支持全雙工通信。這些規范是由 PCI-SIG 開發和維護的,這是 一家由 900 多家公司組成的協會。

PCIe 物理層包括:

● 差分低壓 100 MHz 基準時鐘

● 可 以 擴 充 通 路 寬 度:x1, x2, x4, x8, x12, x16, x32

● 可 以 擴 充 速 度:2.5GT/s (Gen1), 5GT/s (Gen2), 8GT/s (Gen3), 16GT/s (Gen4)

● 在一致性測試中使用不同的連接器,如 CEM、U.2 (SFF-8639)、M.2 或直接焊接到 PCB。

PCI Express— 它用在哪里?

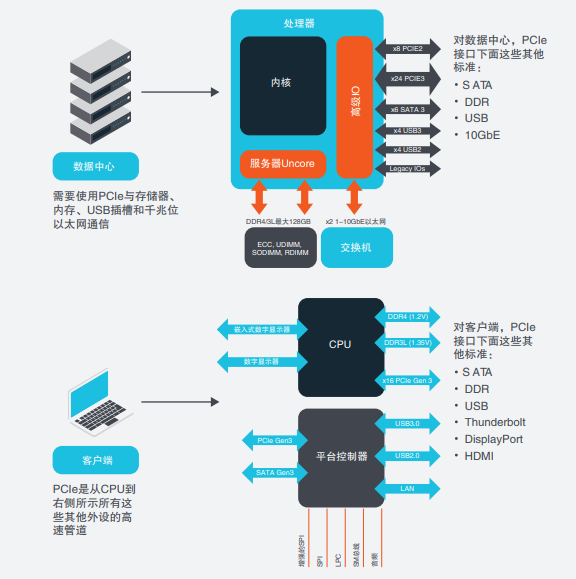

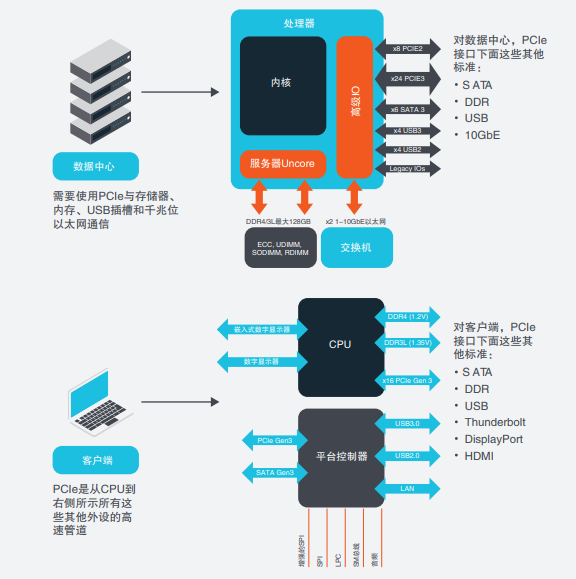

PCIe 是數據中心和客戶端應用中使用的主要的新興高性能存儲和串行總線。PCIe 在外設之間實現了數據通信。 數據中心應用和客戶端應用都有一個核心處理器, 為主機系統上的架構提供原始處理能力。這兩種應用還必須接口各種外設器件,如 SATA 驅動器、 USB 設備等。在跟復合主機與端點器件之間,通常有許多路長損耗通道和連接器,帶來了噪聲、串擾、 定時不規則特點和其他損傷。因此,客戶端和數據中心側的 PCIe 器件必須能夠可靠地演示 PCI 規定的一致性,補償損傷,與 PCIe 器件互操作。

PCIe Gen4 最新進展

由于業界需要提高數據吞吐量和帶寬吞吐量,因此 PCIe 數據速率必須提高,以跟上需求發展步伐。所以 Gen4 中最大的變化之一,是數據速率提高了 2 倍,從 Gen3 的 8GT/s 提高到 Gen4 的 16GT/s。

PCI Express 外形

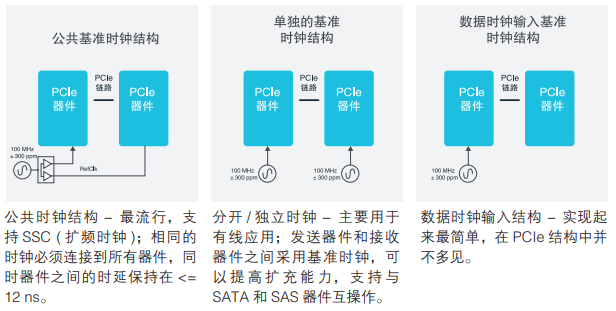

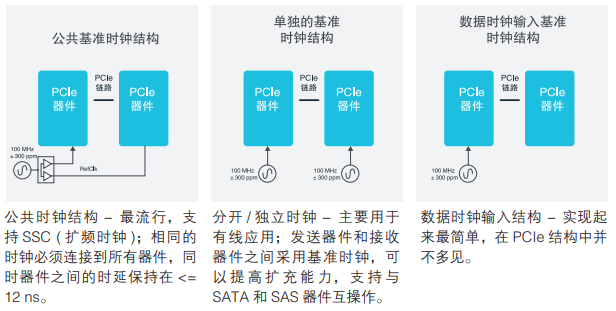

為了方便發射器件和接收器件可靠地傳輸數據,PCI-SIG 對基準時鐘提出了非常嚴格的要求。標準規定使用 100 MHz 時鐘 (Refclk),發射器件和接收器件上的頻率穩定性大于 ±300 ppm,并支持三種不同的時鐘結構,同時協調根復合芯片和端點芯片。

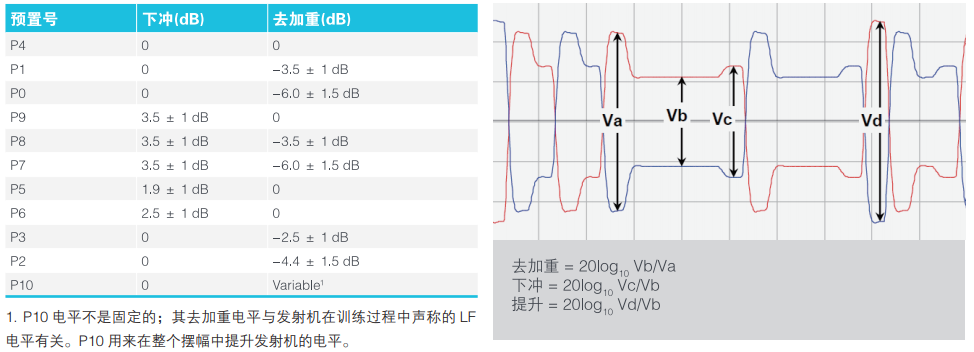

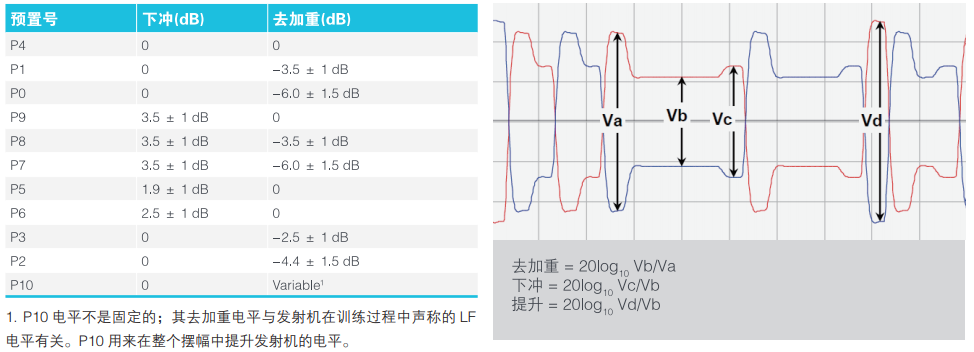

一致性測試預置值

為通過一致性測試,實現互操作,每臺器件都要求進行 PCI-SIG 認證,它基于一個預置值或發射機均衡設置列表,從每秒 2.5 Gb/s 的低 數據速率直到最新的 16 Gb/s 的高數據速率。這些預置值用來均衡通道損耗,優化鏈路上的信號完整性。每個預置值都是主機應用到端 點的下沖和去加重的具體組合。

基本規范發射機 (Tx) 測試

3. 使用高帶寬探頭,探測位置應盡可能靠近發射機引腳 。

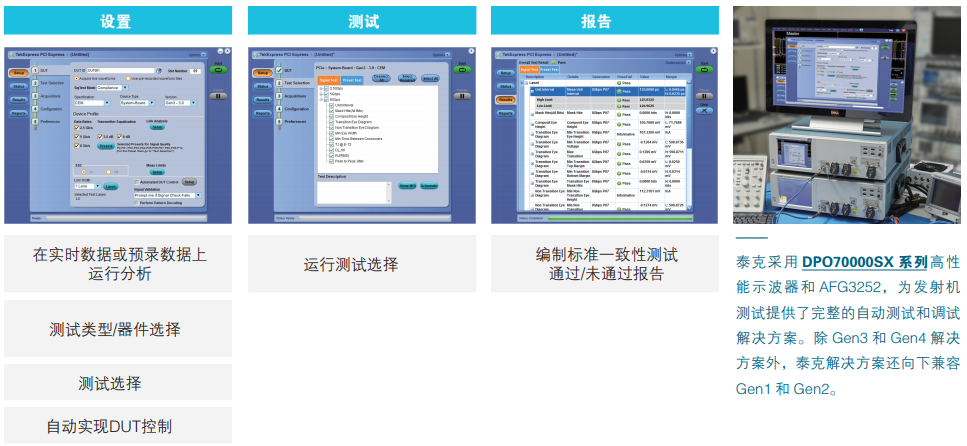

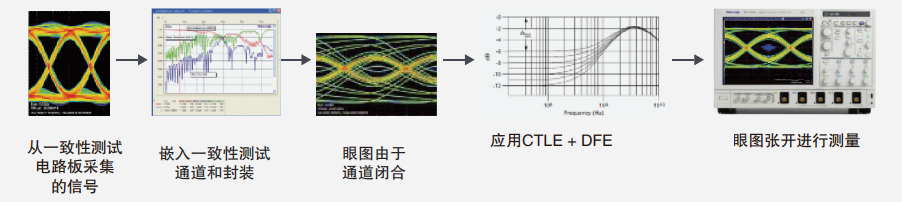

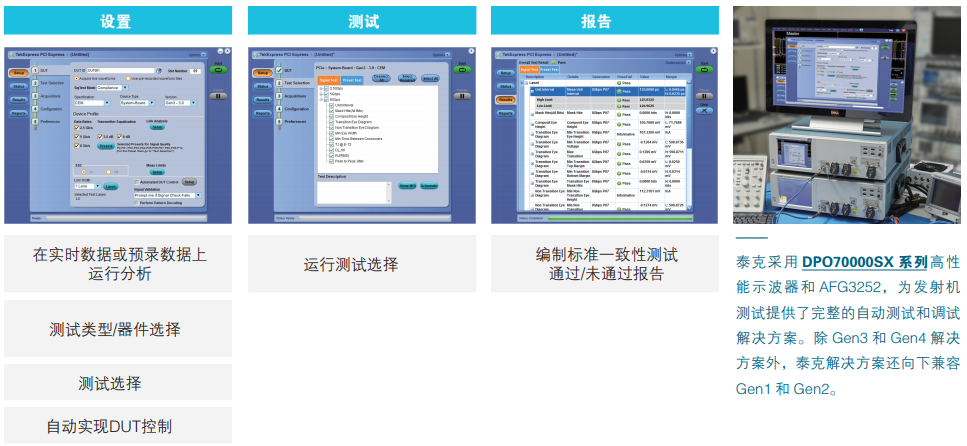

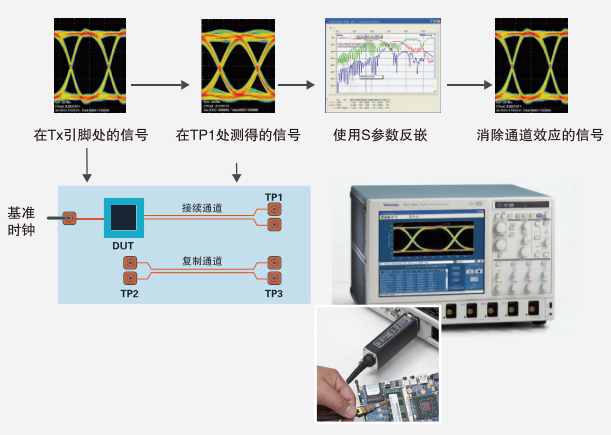

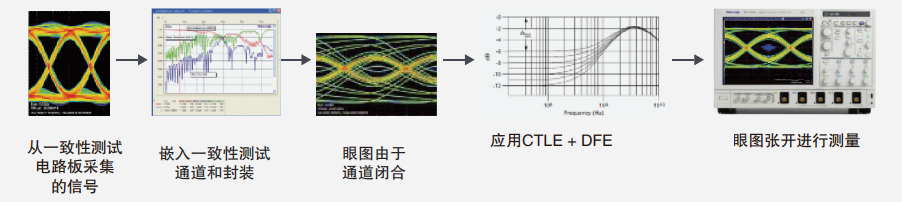

示波器可以使用 SDLA、Seasim 和 SigTest 之類 的軟件工具,執行嵌入 / 反嵌、均衡和眼圖分析。這種軟件級分析允許設計人員在試產前優化和調試芯片性能,節約時間、資金及全面調試。確保采用的測量系統足夠靈活,能夠測試和調試被測器件的特定功能。

CEM 和 U.2 規范發射機 (Tx) 測試

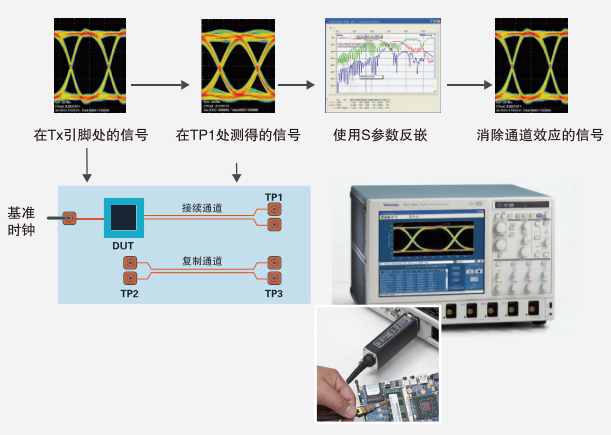

在芯片器件的基本發射機測試中,直接規定了發射機引腳上的測量項目。由于有時不可能接入引腳,因此應在盡可能靠近這個基準點的位置執行測量。

系統和插件在 CEM 級發射機測試中,會像接收機分片器看到的那樣測量發射機的信 號完整性,但由于外形及測試過程中使用的夾具,不可能直接接入信號。為保證測量精度,應實現下面介紹了兩個重要組件。

2. 使用軟件工具應用通道均衡,測量和分析通道末端張開的眼圖。PCISIG 提供了一個軟件工具,稱為 SIG-Test,應用與 PCI-SIG 特性有關的行為均衡器,提供測試通過 / 未通過結果。定制示波器軟件,如泰克 DPOJET 和 SDLA,可以從閉上的眼圖到張開的眼圖,全面表征和調試均衡的信號。

接收機 (Rx) 測試基礎知識

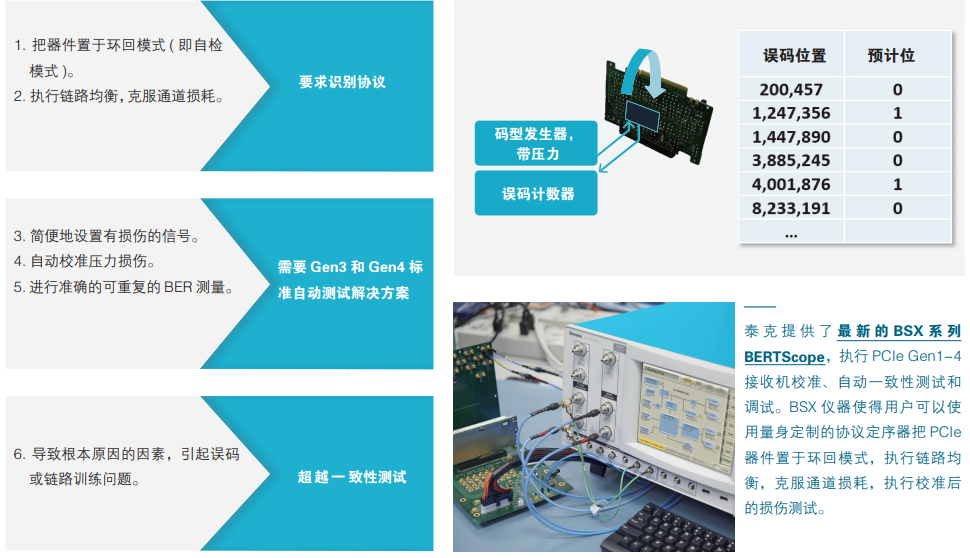

PCIe 測試和調試設置中的關鍵考慮因素

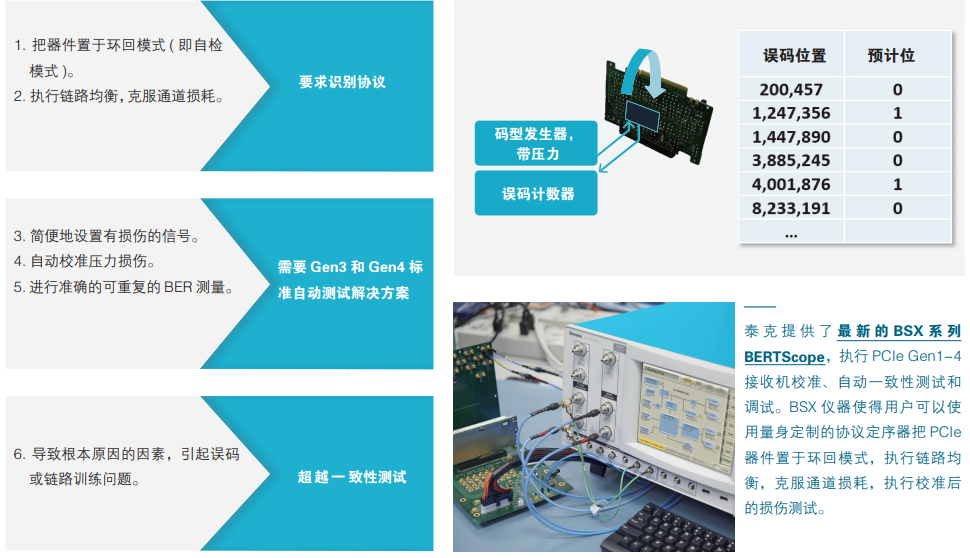

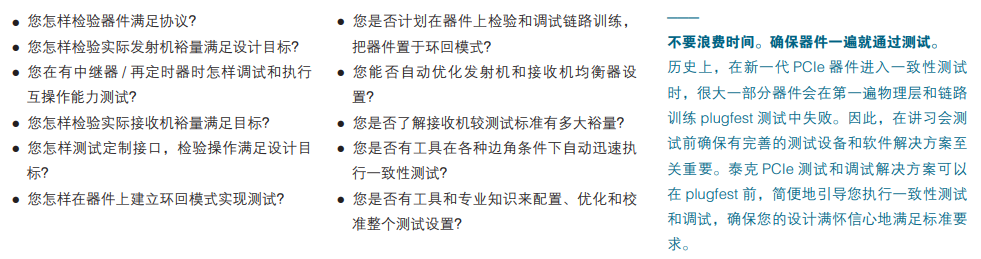

在您處理 Gen3 或 Gen4 PCIe 器件測試和調試前,要問以下幾個關鍵問題:

PCIe 既有串行通信接口,又有存儲接口,這 一點與 SAS 和 SATA 不同,因此實現了額外 的行業擴充能力。PCIe 在跟復合 ( 系統 / 主機 ) 與端點 ( 插件 ) 之間基于點到點總線拓撲,支持全雙工通信。這些規范是由 PCI-SIG 開發和維護的,這是 一家由 900 多家公司組成的協會。

PCIe 物理層包括:

● 差分低壓 100 MHz 基準時鐘

● 可 以 擴 充 通 路 寬 度:x1, x2, x4, x8, x12, x16, x32

● 可 以 擴 充 速 度:2.5GT/s (Gen1), 5GT/s (Gen2), 8GT/s (Gen3), 16GT/s (Gen4)

● 在一致性測試中使用不同的連接器,如 CEM、U.2 (SFF-8639)、M.2 或直接焊接到 PCB。

PCI Express— 它用在哪里?

PCIe 是數據中心和客戶端應用中使用的主要的新興高性能存儲和串行總線。PCIe 在外設之間實現了數據通信。 數據中心應用和客戶端應用都有一個核心處理器, 為主機系統上的架構提供原始處理能力。這兩種應用還必須接口各種外設器件,如 SATA 驅動器、 USB 設備等。在跟復合主機與端點器件之間,通常有許多路長損耗通道和連接器,帶來了噪聲、串擾、 定時不規則特點和其他損傷。因此,客戶端和數據中心側的 PCIe 器件必須能夠可靠地演示 PCI 規定的一致性,補償損傷,與 PCIe 器件互操作。

PCIe Gen4 最新進展

由于業界需要提高數據吞吐量和帶寬吞吐量,因此 PCIe 數據速率必須提高,以跟上需求發展步伐。所以 Gen4 中最大的變化之一,是數據速率提高了 2 倍,從 Gen3 的 8GT/s 提高到 Gen4 的 16GT/s。

PCI Express 外形

為了方便發射器件和接收器件可靠地傳輸數據,PCI-SIG 對基準時鐘提出了非常嚴格的要求。標準規定使用 100 MHz 時鐘 (Refclk),發射器件和接收器件上的頻率穩定性大于 ±300 ppm,并支持三種不同的時鐘結構,同時協調根復合芯片和端點芯片。

一致性測試預置值

為通過一致性測試,實現互操作,每臺器件都要求進行 PCI-SIG 認證,它基于一個預置值或發射機均衡設置列表,從每秒 2.5 Gb/s 的低 數據速率直到最新的 16 Gb/s 的高數據速率。這些預置值用來均衡通道損耗,優化鏈路上的信號完整性。每個預置值都是主機應用到端 點的下沖和去加重的具體組合。

基本規范發射機 (Tx) 測試

3. 使用高帶寬探頭,探測位置應盡可能靠近發射機引腳 。

示波器可以使用 SDLA、Seasim 和 SigTest 之類 的軟件工具,執行嵌入 / 反嵌、均衡和眼圖分析。這種軟件級分析允許設計人員在試產前優化和調試芯片性能,節約時間、資金及全面調試。確保采用的測量系統足夠靈活,能夠測試和調試被測器件的特定功能。

CEM 和 U.2 規范發射機 (Tx) 測試

在芯片器件的基本發射機測試中,直接規定了發射機引腳上的測量項目。由于有時不可能接入引腳,因此應在盡可能靠近這個基準點的位置執行測量。

系統和插件在 CEM 級發射機測試中,會像接收機分片器看到的那樣測量發射機的信 號完整性,但由于外形及測試過程中使用的夾具,不可能直接接入信號。為保證測量精度,應實現下面介紹了兩個重要組件。

2. 使用軟件工具應用通道均衡,測量和分析通道末端張開的眼圖。PCISIG 提供了一個軟件工具,稱為 SIG-Test,應用與 PCI-SIG 特性有關的行為均衡器,提供測試通過 / 未通過結果。定制示波器軟件,如泰克 DPOJET 和 SDLA,可以從閉上的眼圖到張開的眼圖,全面表征和調試均衡的信號。

接收機 (Rx) 測試基礎知識

PCIe 測試和調試設置中的關鍵考慮因素

在您處理 Gen3 或 Gen4 PCIe 器件測試和調試前,要問以下幾個關鍵問題: